## An Effective Embed Algorithm for Newton Fixed-Point Homotopy Method in MOS Transistor Circuits

Dan Niu, Guorui He, Qingshi Ye, Xiaojun Wang, and Xingpeng Zhou

Abstract—Finding the dc operating points is an important task. Recently, an efficient homotopy method termed the Newton fixed-point homotopy method (NFPH) has been proposed to find the dc operating points of MOS transistor circuits. This method is not only efficient but also globally convergent for any initial point. However, how to effectively implement the proposed MOS NFPH method has been an open problem. In this paper, an effective and practical "Embed" implementation algorithm is proposed for the MOS NFPH method. Numerical examples show that the MOS NFPH method with this proposed "Embed" implementation method is more efficient for finding dc operating points than the conventional MOS ATAN-SH method.

Index Terms—DC operating point, homotopy method, SPICE, circuit simulation.

### I. INTRODUCTION

The first step in simulating a transistor circuit is finding its dc operating points. This is a difficult task that involves solving nonlinear algebraic equations describing electronic circuits. The nonlinearities modeling semiconductor devices are of exponential type, and often pose difficulties for numerical solvers. SPICE-like circuit simulators [1], widely utilized for designing LSI's, adopt the Newton-Raphson (NR) method for solving modified nodal (MN) equations. However, due to the local convergence property, the NR method or its variants often fail to converge to a solution unless the initial estimation point is close enough to the solution [2]. To overcome this non-convergence problem, the globally convergent homotopy methods have been studied by many computer-aided design (CAD) researchers from various viewpoints [3]-[8].

These studies are divided into three categories, including how to construct a homotopy function [3]-[9], how to numerically trace a solution curve [10] and how to set an initial solution [11]. Moreover, from the viewpoint of implementation using the existing SPICE-like simulators, there are two types of homotopy functions. The first one, which we call Type I, requires no modifications to the existing device model subroutines, but only additional subroutines, that is, an add-on to the existing circuit simulators. The second one, which we call Type II, does require some modifications to the model subroutines [7]. In

Manuscript received May 7, 2015; revised July 23, 2015. This work was supported in part by the NSF of Jiangsu Province under Grant No. BK20140647, the Priority AcademicProgram Development of Jiangsu Higher Education Institutions and the open fund of Key Laboratory of Measurement and Control of CSE under No. MCCSE2014B03.

All authors are with the Key Laboratory of Measurement and Control of Complex Systems of Engineering, Ministry of Education, Southeast University, Nanjing, 210096 China (e-mail: danniu1@163.com).

SPICE-like simulators, many practical built-in models for semi-conductor devices are contained. These models have been and will be further improved for the advancement of process technologies. Thus the add-on feature is very important for practical implementation. The authors have been studying, from the practical standpoint, the Type I homotopy functions that can be easily implemented [7]. Note that, most previous studies for homotopy methods are mainly focused on the bipolar transistor circuits. At present, the MOS/Bi-MOS transistor circuits are becoming more and more popular in the analog circuit designs. Extending homotopy methods to MOS transistor circuits is important and urgent [12]-[16].

In Ref. [13], a homotopy method based on ATAN-SH Schichman-Hodges) (Arc-tangent is proposed MOS-based mixed-signal circuits. In this homotopy method, two homotopy parameters are used. Due to these two parameters, the simulation becomes complicated and the efficiency is not so satisfactory. In this paper, the Newton fixed-point homotopy method (NFPH) is presented for MOS transistor circuits and it is globally convergent. Moreover, an effective and practical "Embed" algorithm for the MOS NFPH method and an existence theorem of solution curve with this "Embed" algorithm is proposed. At the same time, the initial solution algorithm [11] is also considered during the implementation based SPICE3 simulator, which guarantees high simulation efficiency.

This paper is organized as follows. In Section II, as preliminaries, homotopy method, BDF curve-tracing algorithm and ATANSH-based homotopy method are presented, followed by the proposed effective and practical "Embed" algorithm for the MOS NFPH method in Section III. Numerical examples are shown in Section IV. Finally, the conclusions are summarized.

### II. THE NFPH METHOD FOR MOS TRANSISTOR CIRCUITS

### A. MN Equations of Homotopy Method

We first review homotopy methods for solving systems of nonlinear equations of the form

$$f(x) = 0, \ f(\cdot): \mathbb{R}^n \to \mathbb{R}^n. \tag{1}$$

In the MN equation, Eq. (1) is rewritten as follows [6]:

$$f_{g}(v,i) \square D_{g}g(D_{g}^{T}v) + D_{E}i + J = 0,$$

(2)

$$f_E(v) \square D_E^T v - E = 0, \tag{3}$$

where  $f = (f_g, f_E)^T$  ,  $f_g : R^n \to R^N$  ,  $f_E : R^N \to R^M$  ,

doi: 10.18178/ijiee.2016.6.1.589

$x = (v, i)^T \in R^n$ , and n = N + M. The variable vector  $v \in R^N$  denotes the node voltages to the datum node and the variable vector  $i \in R^M$  denotes the branch currents of the independent voltage sources. Also, the continuous function  $g: R^K \to R^K$  is a VCCS (voltage-controlled current source) type. In addition,  $D_g$  is an  $N \times K$  reduced incidence matrix for the g branches and  $D_E$  is an  $N \times M$  reduced incidence matrix for the independent voltage source branches. Moreover,  $J \in R^N$  is the current vector of the independent current sources and  $E \in R^M$  is the voltage vector of the independent voltage sources.

In homotopy methods, we consider an auxiliary equation

$$f^{0}(x) = 0, \ f^{0}: R^{n} \to R^{n},$$

(4)

with a known solutionx<sup>0</sup> and construct a homotopy

$$h(x,t) = tf(x) + (1-t)f^{0}(x),$$

(5)

where  $h: \mathbb{R}^{n+1} \to \mathbb{R}^n$  and  $t \in [0,1]$  is the homotopy parameter. Then the solution curve of the homotopy equation

$$h(x,t) = 0, (6)$$

is traced from the known initial solution  $(x^0,0)$  at t=0. If the solution curve reaches the t=1 hyper plane at  $(x^*,1)$ , then a solution  $x^*$  to Eq. (1) is obtained [8].

### B. The BDF Curve-Tracing Algorithms

The solution curve of the homotopy equation can be traced by the BDF curve-tracing algorithm [10]. In the BDF algorithm, the solution curve is parameterized by its arc-length *s* and the following system of differential-algebraic equations

$$h(y(s)) = h(x(s), t(s)) = 0,$$

(7)

$$\sum_{i \in I} (x_i(s))^2 + t(s)^2 = 1,$$

(8)

is solved, we can trace the solution curve of (7) and realize the MOS NFPH method [16]. Here,  $I \subseteq \{1, 2, \dots n\}, (|I| = m, m \le n)$  denotes a subset of indices

of the components of x, x = dx/ds and t = dt/ds. Equation (7) is the homotopy equation and Eq. (8) describes the relationship between the arc-length and the components of the solution curve projected into an (m+1)-dimensional Euclidean space. Based on the solution curve-tracing algorithm, the arc length s is regarded as the main variable to steer the simulation. The value t decides whether the simulation should be stopped or not.

### C. The ATANSH-Based Homotopy Method

It is a practical homotopy method for MOS transistor circuits [13]. The ATAN-SH MOS homotopy model is symmetric and bulk referenced. In addition, the model uses two homotopy parameters  $\lambda_1$  and  $\lambda_2$  that take values in [0,

1]. The form of the drain-source current  $I_{ds}$  for the ATAN-SH homotopy method is

$$I_{ds} = \frac{\beta}{2} [V_{gs}(V_{gb}, V_{db}, V_{sb}, \lambda_1, \lambda_2)]^2 h(V_{db} - V_{sb}, \lambda_1), \quad (9)$$

where  $\lambda_1$  controls the drain-source driving-point characteristic while  $\lambda_2$  influences the gate on the drain current, the transfer characteristic [13]. Since there are two homotopy parameters  $\lambda_1$  and  $\lambda_2$ , the homotopy equation h(x,t) are expanded to  $h(x,\lambda_1,\lambda_2)$ ,  $h:R^{n+2}\to R^n$ . Two phases are necessary. Therefore, the simulation becomes complicated and the efficiency for finding the dc operating point is not so satisfactory [15].

# III. THE PROPOSED "EMBED" ALGORITHM OF THE MOS NFPH METHOD

In Ref. [16], the Newton fixed-point homotopy method (NFPH) for MOS transistor circuits is proposed. The auxiliary function is as follows:

$$f^{0}(x) = f(x) - f(x^{0}) + A(x - x^{0}), \tag{10}$$

where A is some  $n \times n$  matrix and represented as follows [16]:

$$A = \begin{bmatrix} D_g G_{FP} D_g^T & 0\\ 0 & -R_{dd} 1_M \end{bmatrix}. \tag{11}$$

In Eq. (11),  $D_g$  is a reduced incidence matrix.  $G_{FP} = diag(G_{FPj})$ ,  $j = 1, 2, \cdots, K$ , is a positive semi-definition diagonal matrix, whose appropriate diagonal elements are positive and the others are zero. Also,  $R_{dd}$  is a scalar positive value and  $\mathbf{1}_M$  is an  $M \times M$  identity matrix.

Then the homotopy is expressed as follows:

$$h(x,t) = f(x) - (1-t)f(x^{0}) + (1-t)(x-x^{0}),$$

(12)

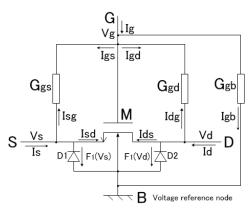

Considering a circuit interpretation of the proposed homotopy function, the term  $(1-t)A(x-x^0)$  is regarded as linear positive resistive elements connected to the original circuit. With respect to A, it further has an interpretation that each conductance element of  $G_{FP}$  is connected in parallel with each branch of appropriate nonlinear branches of g andeach resistance element of  $R_{FP}1_M$  is connected in series with each branch of the independent voltage source branches. For the MOS Newton fixed-point homotopy method, the initial homotopy circuit for a MOS transistor is shown in Fig. 1, which can be obtained by the circuit interpretation at t=0 [16]. In this figure, the conductance elements  $G_{gs}$ ,  $G_{gd}$  and  $G_{gb}$  are connected in parallel with the GS, GD and GB branches of MOS transistor M.

Furthermore, from Eq. (10) and Fig. 1, it is clearly seen that the MOS NFPH method is of Type I [7], which is very

important for practical implementation. Note that, the conductance  $G_{gb}$  between the gate and the body is very important for the global convergence theorems of the MOS NFPH method. Moreover, from the following theorem, the MOS NFPH method is globally convergent. Assuming that the solution curve is smooth, the global convergence theorem of the MOS NFPH method is as follows [16].

Fig. 1. The initial homotopy circuit for a MOS transistor.

Theorem 1: Consider the Newton fixed-point homotopy method for MOS transistor circuits defined by Eqs. (10)-(12). Assume that  $G_{gs}$  and  $G_{gd}$  are sufficient large, then for any initial solution  $x^0 \in R^n$  the solution curve of h(x,t) = 0 starting from  $(x^0,0)$  reaches t=1.

The Proposed "Embed" Implementation Algorithm

In this work, the MOS Newton fixed-point homotopy method is implemented using the source implementation method, which is developed by directly modifying adding and some programs the SPICE3F5simulator. Comparing with the implementation method [8], this source code implementation method is more useful and has higher flexibility for the reason that the Jacobian matrix scale in this implementation method does not be enlarged and the higher efficiency can be obtained.

In this source code implementation method for the MOS NFPH method, how to trace solution curve is quite important. In this work, the BDF curve tracing algorithm (Section II) is used. In the BDF algorithm (Eq. (8)), the arc-length s is regarded as the main variable to steer the simulation. The value t decides whether the simulation should be stopped or not and the value t is changed with s. When the condition t(s) = 1 is satisfied, the homotopy method will stop and the solution of f(x) = 0 can be obtained. In the BDF algorithm, it is much important to build the curve-tracing equation (Eq. (8)). In Eq. (8), the variable  $x_i$  usually uses the node voltages of circuits. However, the dimension of solution curve space will be too large for large-scale circuits. In this paper, the algorithm named "Embed" is proposed to set up the relationship between the circuit variables and the arc s. In this "Embed" algorithm, Eq. (8) is extended as

$$(Px)^{T}(Px) + t^{2} = 1,$$

(13)

where P is some  $(K + M) \times n$  matrix represented as

$$P = \begin{bmatrix} D_g^T & 0\\ 0 & 1_M \end{bmatrix}. \tag{14}$$

It is apparent that  $D_g^T v$  denotes the branch voltage vector for the K branches. Choosing a branch in this way is called setting a "embed" to a branch. Therefore, the solution-tracing variable will employ the branch voltage for the MOS transistor part, which will largely decrease the dimension of solution curve space in large-scale circuits and enhance the efficiency of finding the dc operating points.

Moreover, the proposed "Embed" algorithm for MOS NFPH method is also designed to employ different branches of MOS transistor by setting different P in Eq. (13) to compare the simulation efficiency in our implementation. Here the parameter "embed" is used to denote different branches. As for the MOS transistor circuits, when embed=1, "Embed" is inserted to MOS transistors between the node gate and node drain (GD branch). When embed=2, "Embed" is inserted between the node gate and node source (GS branch). When embed=3, "Embed" is inserted to both the above two positions (GD&GS branches). Furthermore, how implement the proposed "Embed" algorithm in constructing the circuit matrix is as follows. As shown in part A, the homotopy equation Eq. (12) is composed of the original circuit to be solved and the additional terms. Hence, the linearized equation of Eq. (6) can be written as

$$\begin{bmatrix} J_0 & 0 \\ 0 & 0 \end{bmatrix} + J_H \end{bmatrix} \cdot \begin{bmatrix} x \\ t \end{bmatrix} = \begin{bmatrix} b_0 \\ 0 \end{bmatrix} + b_H,$$

(15)

where  $J_0$  and  $b_0$  are the Jacobian matrix and the excitation vector of the original circuit, respectively.  $J_H$  and  $b_H$  are the Jacobian matrix and the excitation vector of Eq. (8) and the additional terms of Eq. (12), respectively. In detail, the additional conductances  $G_{gs}$ ,  $G_{gd}$  and  $G_{gb}$  can be added to the diagonal and minor diagonal positions of circuit Jacobin

matrix  $J_H$ . In Eq. (13), the differential terms x and t will be discretized using the Backward-Euler or Gear numerical integration algorithm and then are added to  $J_H$  and  $b_H$  according to the setting of "embed" parameter. Moreover, the initial solution algorithm [11] is also realized in this source code implementation method.

## IV. NUMERICAL EXAMPLES

In this work, two example circuits are used to verify the effectiveness of our proposed method and they are practically used in analog circuit designs. The MOS NFPH method with our proposed "Embed" implementation algorithm (embed=1, 2, 3) is realized. The SPICE3F5 running on Windows XP operating system (CPU: 2.5GHz, Memory: 4GB, Compiler: Visual C .NET) is applied in our implementations. For comparison, the ATANSH-based homotopy method [13] is also implemented in the same simulation circumstance.

The differential pair circuit (the first example) is a basic

analog circuit component and widely used in monolithic analog circuits. The band gap circuit is commonly used in power supply. More details about the two circuits can be found in [12]. The simulation results of the two MOS circuits are presented in Tables I and Table II.

TABLE I: DIFFERENTIAL PAIR EFFICIENCY COMPARISON

| Differential-pair circuit | Total Iter | Arc Length | Step Num |

|---------------------------|------------|------------|----------|

| ATANSH<br>homotopy        | 161        | 9.4        | 35       |

| NFPH (embed=1)            | 51         | 3.404      | 13       |

| NFPH (embed=2)            | 38         | 1.28       | 10       |

| NFPH (embed=3)            | 52         | 3.48       | 13       |

TABLE II: MOS BANDGAP CIRCUIT EFFICIENCY COMPARISON

| Bandgap circuit    | Total Iter | Arc Length | Step Num |

|--------------------|------------|------------|----------|

| ATANSH<br>homotopy | 306        | 15.86      | 62       |

| NFPH (embed=1)     | 91         | 3.16       | 18       |

| NFPH (embed=2)     | 84         | 1.27       | 16       |

| NFPH (embed=3)     | 84         | 3.21       | 18       |

In Tables I and Table II, three indexes are considered. Here Total Iter means the consumed total iteration number in the simulation. Step Num means the step number when the homotopy parameter t is changed from 0 to 1, and Arc Length is the length of the s resulted from the solution curve-tracing algorithm. Also, there are four rows for each parameter. The row 1 is the result of the ATANSH-based homotopy method. The row 2 is the result of the MOS NFPH method with embed=1 implementation method. The row 3 is the result of embed=2 implementation method and the row 4 is the result of embed=3 implementation method. From the simulation results of the two example circuits, it is clear that the MOS NFPH method with the proposed "Embed" implementation algorithm is more efficient for finding the dc operating points of MOS circuits than the conventional MOS ATAN-SH homotopy method.

### V. CONCLUSIONS

In this paper, an effective and practical "Embed" algorithm has been proposed for implementing the MOS NFPH method on SPICE. Also the existence theorem of a solution curve with the proposed "Embed" algorithm for the MOS NFPH method is proposed. Moreover, the initial solution algorithm is also considered during the implementation based SPICE3 simulator, which guarantees high simulation efficiency. The test results show that our proposed "Embed" implementation algorithm is effective for the MOS NFPH method and the simulation efficiency can been improved greatly compared with the ATANSH-based homotopy method. Therefore, the proposed method will be effective and useful in practical circuit simulation.

#### ACKNOWLEDGMENT

The authors would like to thank Professor Yasuaki Inoue of Waseda University for his assistance.

#### REFERENCES

- L. W. Nagel, "SPICE2: A computer program to simulate semiconductor circuits," Ph.D. dissertation, Univ. California, Berkeley, CA, ERL-M520, May 1975.

- [2] J. M. Ortega and W. C. Rheinboldt, *Iterative Solution of Nonlinear Equations in Several Variables*, Academic Press, 1970, pp. 20-23.

- [3] R. C. Melville, L. Trajkovic, S.-C. Fang, and L. T. Watson, "Artificial parameter homotopy methods for the DC operating point problem," *IEEE Trans. Cornput.-Aided Des. Integrated Circuits & Syst.*, vol. 12, pp. 861-877, June 1993.

- [4] Y. Inoue, "A practical algorithms for DC operating-point analysis of large-scale circuits," *Electronics and Communications in Japan*, vol. 77, no. 10, pp. 49-62, 1994.

- [5] K. Yamamura, T. Sekiguchi, and Y. Inoue, "A fixed-point homotopy method for solving modified nodal equations," *IEEE Trans. Circuits* Syst., vol. 46, no. 6, pp. 654-665, 1999.

- [6] L. B. Goldgeisser and M. M. Green, "A method for automatically finding multiple operating points in nonlinear circuits," *IEEE Trans. Circuits & Syst.*, vol. 52, no. 4, pp. 776-784, 2005.

- [7] Y. Inoue, S. Kusanobu, K. Yamamura, and M. Ando, "A homotopy method using a nonlinear auxiliary function for solving transistor circuits," *IEICE Trans. Inf. & Syst.*, vol. E88-D, no. 7, pp. 1401-1408, 2005

- [8] W. Kuroki and K. Yamamura, "An efficient homotopy method that can be easily implemented on SPICE," *IEICE Trans. Fundamentals*, vol. E89-A, no. 11, pp. 3320-3326, 2006.

- [9] M. Tadeusiewicz and S. Hałgas, "A contraction method for locating all the DC solutions of circuits containing bipolar transistors," *Circuits Syst. Signal Process*, vol. 31, pp. 1159-1166, 2012.

- [10] A. Ushida and L. O. Chua, "Tracing solution curves of nonlinear equations with sharp turning points," Int. J. Circuit Theory & Applications, vol. 12, pp. 1-21, 1984.

- [11] Y. Inoue, S. Kusanobu, K. Yamamura, and M. Ando, "An initial solution algorithm for globally convergent homotopy methods," *IEICE Trans. Fundamentals*, vol. E87-A, no. 4, pp. 780-786, 2004.

- [12] K. Sako, H. Yu, and Y. Inoue, "A globally convergent method for finding DC solutions of MOS transistor circuits," presented at IEEJ International Analog VLSI Workshop 2006, Hangzhou, China, Nov. 16-18, 2006.

- [13] J. Roychowdhury and R. Melville, "Delivering global DC convergence for large mixed-signal circuits via homotopy/continuation methods," *IEEE Trans. Comput.-Aided Des. Integr. Circuits & Syst.*, vol. 25, no. 1, pp. 66-78, 2006.

- [14] H. Vazquez-Leal, B. Benhammouda, K. Boubaker, Y. Khan, U. Filobello-Nino, R. Castaneda-Sheissa, and R. Ruiz-Gomez, "Homotopy-based direct current analysis with formal stop criterion," in *Proc. IEEE 57th MWSCAS*, 2014, pp. 1009-1012.

- [15] D. Niu, S. Kazutoshi, G. M. Hu, and Y. Inoue, "A globally Convergence nonlinear homotopy method for MOS transistor circuits," *IEICE Trans. Fundamentals*, vol. E95-A, no. 12, pp. 2251-2260, 2012.

- [16] D. Niu, X. Wu, Z. Jin, and Y. Inoue, "An effective and globally convergent Newton fixed-point homotopy method for MOS transistor circuits," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. E96-A, no. 9, pp. 1848-1856, 2013.

Dan Niu was born on April 16, 1986 in Jiangsu province, China. He received the B.E. degree in automation from Hohai University, Nanjing, China, in 2007. He received M.E. degree in automation from Southeast University, Nanjing, China, in 2010. He received the Doctor degree at Graduate School of Information, Production and Systems, Waseda University, Kitakyushu, Japan, in 2013. Since 2013, he has been an assistant professor at the School of Automation, Southeast University. His research interests

include verification technologies for nonlinear circuits and systems, LSI simulation technologies, analog circuit and embedding system designs and wireless communications.

**Guorui He** was born on July 22, 1991 in Jiangsu province, China. He received the B.E. degree in automation from Southeast University, Nanjing, China, in 2013. He is now pursuing the M.E. degree at the school of Automation, Southeast University, Nanjing, China. His research interests include analog circuit, embedding system designs and wireless communications.

Qingshi Ye was born on December 24, 1992 in Fujian province, China. He received the B.E. degree in automation from Southeast University, Nanjing, China, in 2014. He is now pursuing the M.E. degree at the school of Automation, Southeast University, Nanjing, China. His research interests include analog circuit and embedding system designs.

Xiaojun Wang was born on December 3, 1975 in Jiangsu province, China. He received the B.E. degree in automation from Southeast University, Nanjing, China, in 1996. He received M.E. degree in automation from Southeast University, Nanjing, China, in 2002. He received the Doctor degree in automation from Southeast University, Nanjing, China, in 2006. Since 2007, he has been an assistant professor in the School of Automation,

Southeast University. His research interests include analog circuit and embedding system designs and wireless communications.

Xingpeng Zhou was born on December 23, 1951 in Jiangsu province, China. He received the B.E. degree in automation from Southeast University, Nanjing, China, in 1978. He received M.E. degree in automation from Southeast University, Nanjing, China, in 1982. Since 1997, he has been a professor at the School of Automation, Southeast University. His research interests include analog circuit and embedding system designs and

wireless communications.